University of Southern California

# EE582 Lab Report #3

HONGXIANG GAO 8095639536 University of Southern California July 14, 2019

# Contents

| 1 | Introductio       | n                                | 2 |

|---|-------------------|----------------------------------|---|

| 2 | Schematic         | of Circuit                       | 2 |

| 3 | Simulation Result |                                  | 3 |

|   | 3.0.1             | Functionality                    | 3 |

|   | 3.0.2             | Supply & Temperature Fluctuation | 4 |

|   | 3.0.3             | Continuous Input AP              | 6 |

#### 1 Introduction

A neural synapse circuit design is presented here. The circuit models the result of an action potential applied to a biological synapse, including neurotransmitter action, membrane potentials, and ion pumps. The synapse is one of the most important parts of a neuron.[1]

### 2 Schematic of Circuit

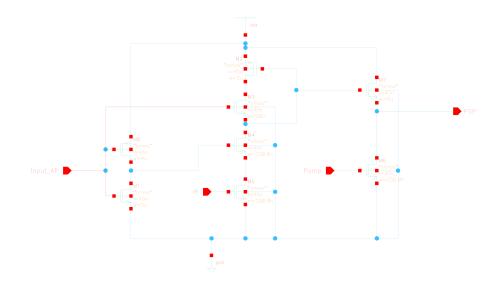

Figure 1: Schematic of Synapse Circuit

Figure 1 shows the schematic of the synapse circuit. The fabrication technology used in this circuit is 45nm. And for each MOSFET, the reasons of sizing are given below. The circuit has the pre-synapse and post-synapse structure.

For M4, M5 and M6, they are sized as very small to decrease its strength for pulling down which can give a proper falling time, say 10 times about the falling time of the input AP.

For M3, it is sized as very large to get a strong strength for pulling up the signal and tuning up the EPSP signal as 20% of input AP.

For the remain PMOS and NMOS, they are sized as normal sizing as in Axon Hilock circuit, which is  $5\mu$ m for NMOS and  $4\mu$ m for PMOS.

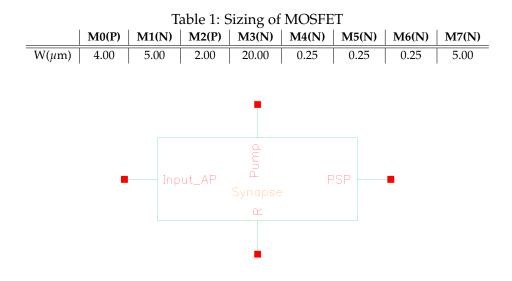

Figure 2 shows the symbol of the synapse circuit. It has three inputs, Input AP, R and Pump, the output is PSP.

Ħ)

Figure 2: Symbol of Synapse Circuit

### **3** Simulation Result

#### 3.0.1 Functionality

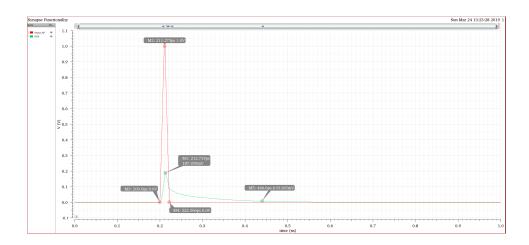

Figure 3: Functionality Test of Synapse Circuit

Figure 3 shows the functionality test of the synapse circuit. The amplitude of the input AP is 1V and its duration is about 22ps, as simulated in the Axon Hilock circuit. The output signal has an amplitude of 187mV, which is about 20% of the input signal. And its duration is more than 440ps, which is more than 10 times of the input duration.

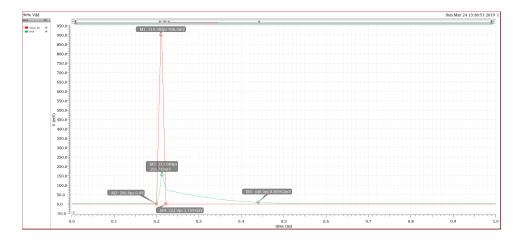

#### 3.0.2 Supply & Temperature Fluctuation

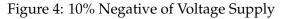

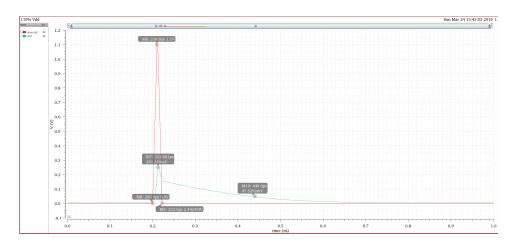

Figure 5: 10% Positive of Voltage Supply

Figure 4 and 5 show the circuit performance when the voltage supply fluctuates 10%. For negative fluctuation, the amplitude of the output signal decreases a little bit, which is about 17% of the input signal, while for positive fluctuation, its amplitude is about 23% of the input signal. For duration, both of cases can reach the 10 times of the input duration, while positive fluctuation case has a much longer duration.

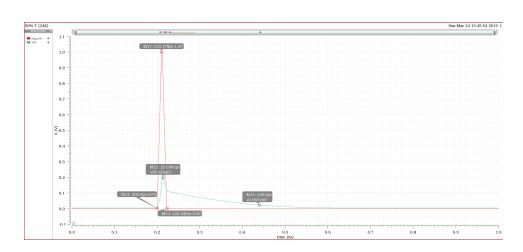

Figure 6: 10% Negative of Temperature

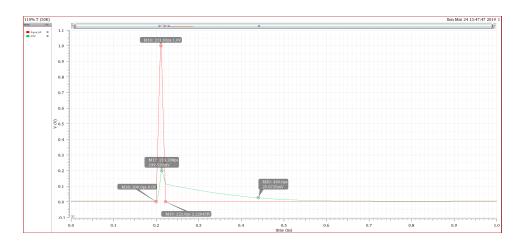

Figure 7: 10% Positive of Temperature

Figure 6 and 7 show the circuit performance when the temperature fluctuates 10%. For normal temperature, it is set as 27 degrees, then for 10 % fluctuation, I take 3 degrees as change. For negative fluctuation, the duration of the output signal increases a little bit, while for positive fluctuation, its duration decreases a little bit. But both of them still can fit the requirement of 10 times to the input signal. For amplitude, both of cases are about 20% of the input signal.

#### 3.0.3 Continuous Input AP

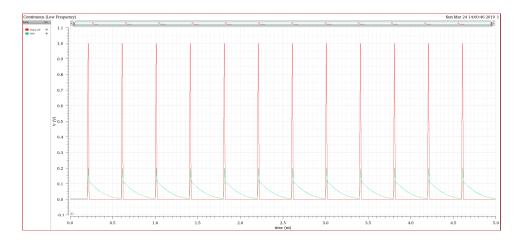

Figure 8: Continuous Input AP with Low Frequency

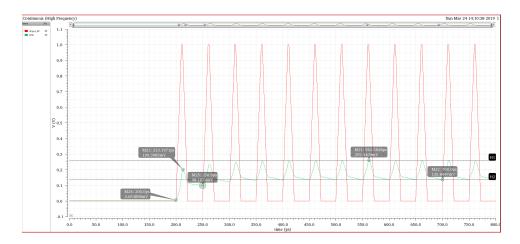

Figure 9: Continuous Input AP with High Frequency

Figure 8 and 9 show the circuit performance with continuous input AP signal with different frequency. For low frequency, which is about 400ps as the period, the output signal is like the replication of the normal output signal. For high frequency input, the period is about 50ps, the output is quite different with the previous one. The frequency of the output signal is the same as the input signal. And since the normal duration is much longer than this period, the synapse doesn't have enough time to pull down the potential, so the amplitude of the output, say  $V_{HIGH} - V_{LOW}$  is about 120mV, and the offset is lifted from 0 to about 200mV.

# References

1. Aaron K Friesz, Alice C Parker, Chongwu Zhou, Koungmin Ryu, Jason M Sanders, H-S Philip Wong, and Jie Deng. A biomimetic carbon nanotube synapse circuit. In *Biomedical Engineering Society (BMES) Annual Fall Meeting*, volume 2, page 29, 2007.